Микроархитектура NetBurst

Повышение производительности IA-32 достигалось не только путем оптимизации конвейера команд и добавления исполнительных блоков, но и, например, внедрением кэш-памяти в ядро процессора. В семействе IA-32 встроенный кэш L1 размером 8 Кбайт впервые был реализован в процессорах Intel-486. В процессорах Pentium размер кэша был удвоен. Первые представители P6 (Pentium Pro) содержали также кэш L2 размером 256 или 512 Кбайт. Однако такое решение в то время оказалось слишком дорогим и невыгодным, поэтому в Pentium II была представлена технология Dual Independent Bus (DIB) - двойная независимая шина. Процессор выполнялся в виде картриджа с печатным краевым разъемом, на который выведена системная шина. На картридже размером 14х6,2х1,6см устанавливались микросхема ядра процессора (CPU Core), несколько микросхем, реализующих вторичный кэш, и вспомогательные дискретные элементы (резисторы и конденсаторы). Удаление вторичного кэша из кристалла процессора позволило использовать для кэш-памяти и памяти тегов микросхемы сторонних производителей, специализирующихся на выпуске сверхбыстродействующей памяти. Объем вторичного кэша определялся емкостью и числом установленных микросхем памяти. Для доступа к кэшу и для доступа к внешней памяти использовались раздельные шины. Такое же архитектурное решение использовалось в первых моделях Pentium III. Начиная с 1999 года (Pentium III Coppermine), кэш L2 вновь был возвращен внутрь кристаллов процессоров.

Процессор Pentium 4 является 32-разрядным представителем семейства IA-32, по микроархитектуре принадлежащим к новому, седьмому (по классификации Intel) поколению. С программной точки зрения он представляет собой процессор IA-32 с очередным расширением системы команд - SSE2. По набору программно-доступных регистров Pentium 4 повторяет процессор Pentium III. С внешней, аппаратной точки зрения - это процессор с системной шиной нового типа, в которой кроме повышения тактовой частоты применены ставшие уже привычными принципы двойной (2х) и четырехкратной (4х) синхронизации, а также предпринят ряд мер по обеспечению работоспособности на ранее немыслимых частотах.

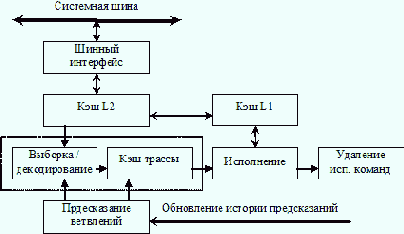

Микроархитектура процессора, получившая название NetBurst, разработана с учетом высоких частот как ядра (>1,4 ГГц), так и системной шины (400 МГц). Название микроархитектуры указывает на сетевую направленность процессора: его мощь необходима для ресурсоемких мультимедийных Интернет-приложений.

Процессор Pentium 4 является однокристальным. Кроме собственно вычислительного ядра, он содержит кэш-память двух уровней. Вторичный кэш, общий для инструкций и данных, имеет размер 256 Кбайт и разрядность шины 256 бита (32 байта), как и в последних процессорах Pentium III. Шина вторичного кэша работает на частоте ядра, что обеспечивает ее пропускную способность 32х1,4 = 44,8 Гбайт/с на частоте 1,4 ГГц. Вторичный кэш имеет ЕСС-контроль, позволяющий обнаруживать и исправлять ошибки. Первичный кэш данных имеет такую же высокую пропускную способность (44,8 Гбайт/с), но его объем сократился вдвое (8 Кбайт против 16 в Pentium III). Первичный кэш инструкций в привычном понимании отсутствует, его заменил кэш трассы (trace cache). В нем хранятся последовательности микроопераций, в которые декодированы инструкции. Здесь могут помещаться до 12К микроинструкций.

Интерфейс системной шины процессора рассчитан только на однопроцессорные конфигурации, отсутствует также возможность избыточного функционального контроля (FRC). Интерфейс во многом напоминает шину Р6, протокол также ориентирован на одновременное выполнение нескольких транзакций. Принят ряд мер по обеспечению высокой пропускной способности. В процессоре Pentium 4 частота шины 400 МГц с "четырехкратной накачкой" (quad pumped) - тактовая частота системной шины составляет 100 МГц, но частота передачи адресов и данных выше. Новая информация по линиям с общей синхронизацией может передаваться на каждом такте с частотой 100 МГц. Для 2 и 4-кратной передачи используется синхронизация от источника данных. По шине адреса информация передается в режиме 2-кратной передачи, стробами являются два сигнала ADSTB0# и ADSTB1#. По спаду этих стробов передается адрес, а по фронту - информация о типе транзакции.

Таким образом, в каждом такте шины (за 10 нс) передается и адрес, и тип транзакции ( у Р6 на это требовалось 2 такта, что занимало 15-30 нс). По шине данных информация передается с четырехкратной частотой, для чего используются пары стробирующих сигналов DSTBp[0:3]# и DSTBn[0:3]# с периодом 5 нс (частота 200 МГц). Стробы сдвинуты относительно друг друга на 2,5 нс (половину своего маленького такта), синхронизация по их спадам и дает учетверенную частоту передачи.

Разрядность шины данных, как и в предыдущих двух поколениях процессоров, составляет 64 бита (8 байт), что в режиме 4-кратной передачи дает максимальную пропускную способность 100х4х8=3,2 Гбайт/с. У процессоров Pentium III шина обеспечивала 133х8=1,06 Гбайт/с. Шина адреса имеет разрядность 36 бит, и это позволяет адресовать те же 64 Гбайт памяти, из которых кэшируются только первые 4 Гбайт.

Исполнительные устройства МП (АЛУ) работают на удвоенной частоте, что дает возможность выполнять большинство целочисленных инструкций за половину такта. По сравнению с предыдущими поколениями IA-32, Pentium 4 содержит самый длинный конвейер команд, состоящий из 20 этапов и названный гиперконвейером. В связи с этой особенностью многие специалисты отмечают, что микроархитектура NetBurst будет иметь максимальную производительность исполнения предсказуемых (линейных и циклических) участков программы, характерных для приложений, на которые ориентирован Pentium 4. На непредсказуемо ветвящихся программах, к которым относятся, например, офисные приложения, длинный гиперконвейер оказывается менее эффективным, чем конвейер Р6, если бы тот удалось разогнать до частот 1,4 ГГц и выше. Чтобы частично компенсировать этот недостаток, были существенно оптимизированы механизмы спекулятивного исполнения и предсказания ветвлений.

Рис. 6.2. Микроархитектура NetBurst